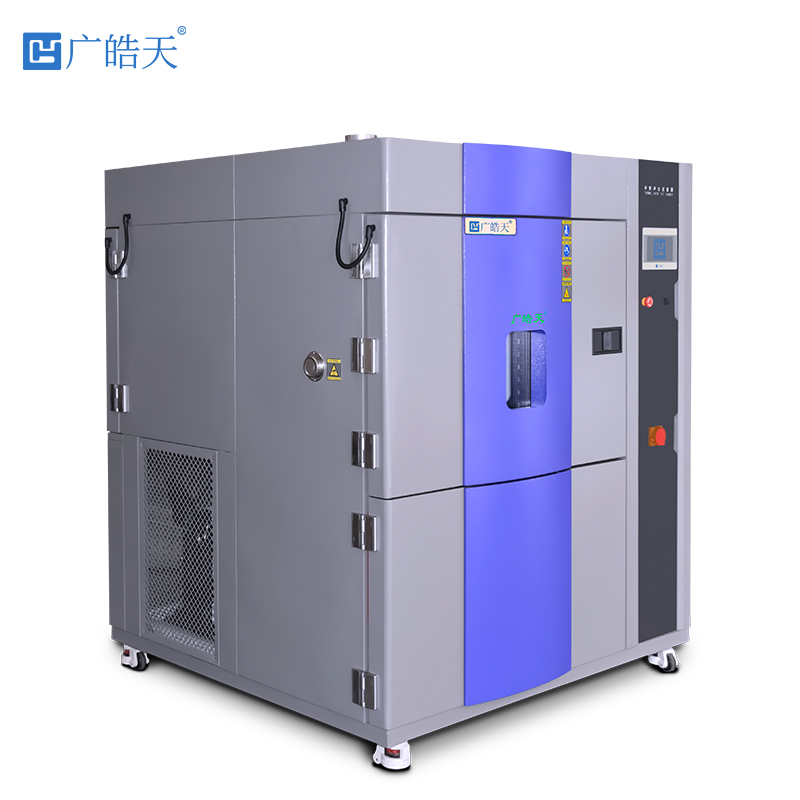

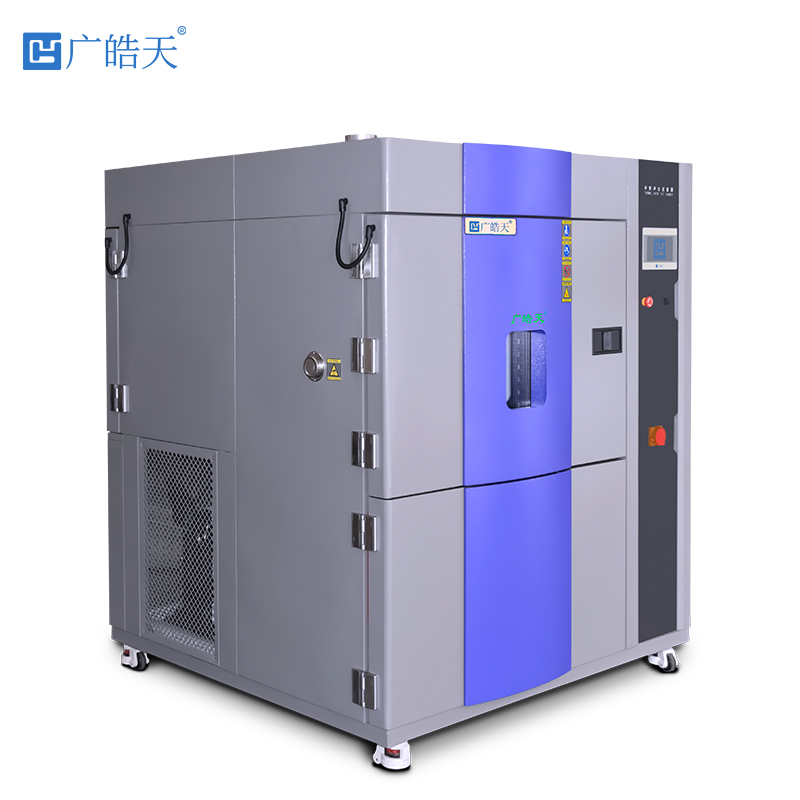

半导体芯片可靠性测试新方案 —— 三箱式温度冲击试验箱的过渡缓冲技术与实操指南

在 5G 通信、新能源汽车等高级领域推动下,半导体芯片需承受极限温度波动考验。三箱式温度冲击试验箱凭借 “高温箱 - 过渡箱 - 低温箱" 三槽结构,通过缓冲过渡实现温和冲击,成为封装后芯片可靠性验证的核心设备,其测试结果直接决定芯片能否满足 JEDEC 等严苛标准。

一、设备核心特性与技术优势

三箱式设备的核心竞争力在于过渡缓冲设计,相比两箱式直接切换,过渡箱可避免温度骤变对芯片封装的机械损伤。其技术参数精准匹配芯片测试需求:高温箱采用镍铬合金加热管,控温范围 - 70℃~+170℃,部分高级机型可达 - 90℃~+225℃,温度精度 ±0.5℃,波动度≤0.3℃,满足车规芯片 - 55℃~+150℃的测试需求;低温箱依托复叠式制冷系统,降温速率达 60℃/min,配合过渡箱可将转换时间控制在≤5 秒,且温度过冲≤±2℃。

设备集成化测试能力显著:内置 64 路信号采集通道,支持漏电流(nA 级)、导通电阻(mΩ 级)等芯片核心参数监测,采样频率 0.1Hz~10kHz 可调;控制系统兼容 JEDEC JESD22-A104-b 标准,可预设 96 组试验程序,支持 50~1000 次循环自动运行,同步生成温度 - 电性能关联曲线。过渡箱的气流缓冲设计,使芯片在高低温切换时承受的热应力降低 40%,尤其适配 SiC、GaN 等宽禁带半导体的精密测试。

二、半导体芯片测试标准流程

(一)试验前准备

样品处理需严格遵循 “筛选 - 固定 - 校准" 三步法:选取 8~10 颗同批次封装芯片,先通过 CP 测试(晶圆测试)剔除裸片缺陷,再经 FT 测试(成品测试)验证初始电性能,确保漏电流、击穿电压等参数符合 SPEC 要求;采用防静电陶瓷夹具固定芯片,引脚通过探针卡连接测试系统,避免金属夹具导热干扰;使用精度 ±0.1℃的标准铂电阻校准箱内传感器,并用示波器校准信号采集模块,误差控制在 ±0.5% 以内。

(二)参数设定与执行

依据芯片类型差异化配置参数:消费类 MCU 测试设定高温 125℃、低温 - 40℃,驻留时间 15 分钟,循环 50 次;车规功率芯片需提升至高温 150℃、低温 - 55℃,驻留时间延长至 30 分钟,循环 200 次,模拟发动机舱极限环境。试验执行遵循 “高温暴露 - 过渡缓冲 - 低温暴露" 闭环:芯片先在高温箱达到热平衡,经过渡箱(温度梯度≤10℃/ 秒)缓冲后进入低温箱,每 50 次循环进行中间检测,排查封装裂纹与参数漂移。

(三)结果判定体系

试验结束后实施三级检测:外观层面,通过 X 射线与声学扫描显微镜检查,无封装开裂、焊点脱落等物理缺陷为合格;电性能层面,在常温、高温、低温三温点测试,要求漏电流变化量≤10%、击穿电压偏移率<2%;稳定性层面,常温静置 72 小时后复测,参数漂移≤1% 且功能无异常。三级检测均达标则判定通过,任一环节失效需通过 SEM 分析失效机理,优化封装工艺。

三、关键问题与解决方案

(一)温度均匀性偏差

高温箱局部温差>±3℃会导致芯片受热不均,需采用双风机对称送风结构,在芯片阵列周围布置 4 个监测点,温差超 ±1.5℃时自动调节风道挡板。每月清洁加热管与滤网,避免灰尘堆积造成的局部过热,使温度均匀性提升至 ±1℃以内。

(二)电信号干扰

制冷系统电磁辐射易引发测试数据波动,需构建三重防护:信号线缆采用铜网 + 铝箔双层屏蔽,探针卡接地电阻<1Ω;采集模块采用 24V 独立稳压电源,与主电源隔离;数据处理引入 10ms 滑动平均滤波算法,剔除瞬时干扰信号。

(三)热滞后效应

芯片内部结温与表面温度差可能达 15℃,需借助 TCAD 仿真计算热平衡时间,在此基础上延长 20% 驻留时间。对功率芯片可植入 DS18B20 微型传感器,实时监测结温,待结温与箱温偏差≤2℃时再切换环境,确保测试真实性。

更新时间:2025-10-15

更新时间:2025-10-15  浏览次数:240

浏览次数:240